SLUS846A-SEPTEMBER 2008-REVISED MARCH 2009

# 8-Pin High-Performance Resonant Mode Controller

### FEATURES

- Variable Switching Frequency Control

- Programmable Minimum Switching Frequency With 4% Accuracy (3% accuracy at temperature range: -20°C to 105°C)

- Programmable Maximum Switching Frequency

- Programmable Dead Time for Best Efficiency

- Programmable Soft-Start Time

- Easy ON/OFF Control

- Over-Current Protection

- Over-Temperature Protection

- Bias Voltage UVLO and OVP

- Integrated Gate Driver With 0.4-A Source and 0.8-A Sink Capability

- Operating Temperature Range: -40°C to 125°C

- SOIC 8-Pin Package

### **APPLICATIONS**

- 100-W to 1-kW Power Supplies

- LCD, Plasma and DLP TVs

- Adaptors, Computing and ATX Power Supplies

- Home Audio Systems

- Electronic Lighting Ballasts

### DESCRIPTION

The UCC25600 high performance resonant mode controller is designed for dc-to-dc applications utilizing resonant topologies, especially the LLC half bridge resonant converter. This highly integrated controller implements frequency modulation control and complete system functions in only an 8-pin package. Switching to the UCC25600 will greatly simplify the system design, layout and improve time to market, all at a price point lower than competitive 16-pin device offerings.

The internal oscillator supports the switching frequencies from 30 kHz to 350 kHz. This high accuracy oscillator realizes the minimum switching frequency limiting with 4% tolerance, allowing the designer to avoid "over design" of the power stage and, thus, further reducing overall system cost. The programmable dead time enables zero-voltage switching with minimum magnetizing current. This will maximize system efficiency across a variety of applications. The programmable soft-start timer maximizes design flexibility demanded by the varied requirements of end equipments utilizing a half bridge topology. By incorporating 0.4-A source and 0.8-A sink driving capability, a low cost, reliable gate driver transformer is a real option.

The UCC25600 delivers complete system protection functions including over current, UVLO, bias supply OVP and over temperature protection.

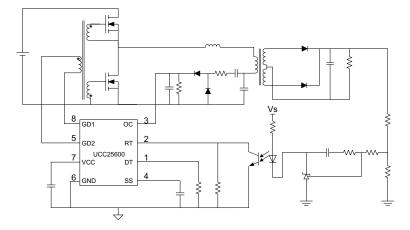

# TYPICAL APPLICATION DIAGRAM

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

www.ti.com

#### **ORDERING INFORMATION**

| PART NUMBER | PACKAGE    | OPERATING TEMPERATURE |

|-------------|------------|-----------------------|

| UCC25600D   | 8-Pin SOIC | -40°C to 125°C        |

### ABSOLUTE MAXIMUM RATINGS<sup>(1)(2)(3)(4)</sup>

over operating free-air temperature range (unless otherwise noted)

| PARAMETER                                      | LIMIT             | UNIT |

|------------------------------------------------|-------------------|------|

| Supply voltage, VCC                            | 22                | V    |

| Voltage, GD1, GD2                              | -0.5 to VCC + 0.5 | V    |

| Gate drive current – continuous, GD1, GD2      | +/- 25            |      |

| Current, RT                                    | -5                | mA   |

| Current, DT                                    | -0.7              |      |

| Operating junction temperature, T <sub>J</sub> | -40 to 125        |      |

| Storage temperature, T <sub>STG</sub>          | -65 to 150        | °C   |

| Lead temperature (10 seconds)                  | 260               |      |

(1) These are stress limits. Stress beyond these limits may cause permanent damage to the device. Functional operation of the device at these or any conditions beyond those indicated under RECOMMENDED OPERATING CONDITIONS is not implied. Exposure to absolute maximum rated conditions for extended periods of time may affect device reliability.

All voltages are with respect to GND.

All currents are positive into the terminal, negative out of the terminal. (3)

(4) In normal use, terminals GD1 and GD2 are connected to an external gate driver and are internally limited in output current.

### **ELECTROSTATIC DISCHARGE (ESD) PROTECTION**

| PARAMETER                  | RATING | UNIT |

|----------------------------|--------|------|

| Human Body Model (HBM)     | 2,000  | N/   |

| Charged Device Model (CDM) | 500    | V    |

### **DISSIPATION RATINGS**

| PACKAGE    | THERMAL IMPEDANCE,<br>JUNCTION-TO-AMBIENT | T <sub>A</sub> = 25°C POWER RATING | T <sub>A</sub> = 85°C POWER RATING |

|------------|-------------------------------------------|------------------------------------|------------------------------------|

| 8-Pin SOIC | 150°C/watt <sup>(1)(2)</sup>              | 667 mW <sup>(1)</sup>              | 267 mW <sup>(1)</sup>              |

Thermal resistance is a strong function of board construction and layout. Air flow will reduce thermal resistance. This number is only a (1) general guide. Thermal resistance calculated with a low-K methodology.

(2)

### **RECOMMENDED OPERATING CONDITIONS**

over operating free-air temperature range (unless otherwise noted)

| PARAMETER                                     | MINIMUM | MAXIMUM | UNIT |

|-----------------------------------------------|---------|---------|------|

| VCC input voltage from a low-impedance source | 11.5    | 18.0    | V    |

| RT resistance                                 | 1       | 8.666   | kO   |

| DT resistance                                 | 3.3     | 39      | kΩ   |

| SS capacitor                                  | 0.01    | 1       | μF   |

### **ELECTRICAL CHARACTERISTICS**

over operating free-air temperature range,  $-40^{\circ}C < T_A < 125^{\circ}C$ ,  $T_J = T_A$ , VCC = 12 V, GND = 0 V,  $R_{RT} = 4.7 \text{ k}\Omega$ ,  $R_{DT} = 16.9 \text{ k}\Omega$ ,  $C_{VCC} = 1 \mu$ F, (unless otherwise noted)

| SYMBOL                 | PARAMETER                                     | TEST CONDITIONS                                                        | MIN   | ТҮР   | MAX   | UNITS |  |

|------------------------|-----------------------------------------------|------------------------------------------------------------------------|-------|-------|-------|-------|--|

| Bias Suppl             | ly (VCC)                                      | · · · · ·                                                              |       | P     |       |       |  |

|                        | VCC current, disabled                         | SS = 0 V                                                               |       | 1     | 1.5   |       |  |

|                        | VCC current, enabled                          | $SS = 5 V, C_{GD1} = C_{GD2} = 1 nF$                                   | 2.5   | 5     | 7.5   | mA    |  |

|                        | VCC current, UVLO                             | VCC = 9 V                                                              |       | 100   | 400   | μA    |  |

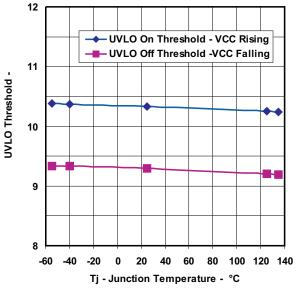

|                        | UVLO turn-on threshold                        | Measured at VCC rising                                                 | 9.9   | 10.5  | 11.1  |       |  |

| V <sub>UVLO</sub>      | UVLO turn-off threshold                       | Measured at VCC falling                                                | 8.9   | 9.5   | 10.1  |       |  |

|                        | UVLO hysteresis                               | Measured at VCC                                                        | 0.7   | 1     | 1.3   | V     |  |

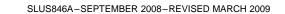

|                        | OVP turn-off threshold                        | Measured at VCC rising                                                 | 18    | 20    | 22    | v     |  |

| V <sub>OVP</sub>       | OVP turn-on threshold                         | Measured at VCC falling                                                | 16    | 18    | 20    |       |  |

|                        | OVP hysteresis                                | Measured at VCC                                                        | 1.5   | 2     | 2.5   |       |  |

| Dead Time              | (DT)                                          |                                                                        |       |       |       |       |  |

| T <sub>DT</sub>        | Dead time                                     | R <sub>DT</sub> = 16.9 kΩ                                              | 390   | 420   | 450   | ns    |  |

| Oscillator             |                                               |                                                                        |       |       |       |       |  |

| E                      | Minimum switching frequency at                | -40°C to 125°C                                                         | 40.04 | 41.70 | 43.36 | kHz   |  |

| F <sub>SW(min)</sub>   | GD1, GD2                                      | -20°C to 105°C                                                         | 40.45 | 41.70 | 42.95 | NI IZ |  |

| K <sub>ICO</sub>       | Switching frequency gain/I (RT)               | $R_{RT} = 4.7 \text{ k}\Omega$ , $I_{RT} = 0 \text{ to } 1 \text{ mA}$ | 60    | 80    | 100   | Hz/μA |  |

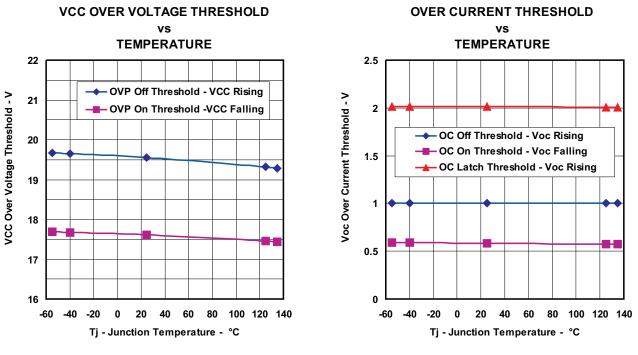

|                        | GD1, GD2 on time mismatching                  |                                                                        | -50   |       | 50    | ns    |  |

| F <sub>SW_BM</sub>     | Switching frequency starting burst mode       | SS = 5 V                                                               | 300   | 350   | 400   |       |  |

|                        | Switching frequency to come out of burst mode | SS = 5 V                                                               | 280   | 330   | 380   | kHz   |  |

| -                      | Quitabing fragman at a ft start               | -40°C to 125°C                                                         | 122   | 142.5 | 162   |       |  |

| F <sub>SW(start)</sub> | Switching frequency at soft start             | -20°C to 105°C                                                         | 125   | 142.5 | 160   |       |  |

| External Di            | isable/Soft Start                             |                                                                        |       |       |       |       |  |

|                        | Enable threshold                              | Measure at SS rising                                                   | 1.1   | 1.2   | 1.3   |       |  |

|                        | Disable threshold                             | Measured at SS falling                                                 | 0.85  | 1     | 1.1   | V     |  |

|                        | Disable hysteresis                            | Measured at SS                                                         | 0.15  |       | 0.35  |       |  |

|                        | Disable prop. delay                           | Measured between SS (falling) and GD2 (falling)                        | 250   | 500   | 750   | ns    |  |

|                        | Source current on ISS pin                     | V <sub>SS</sub> = 0.5 V                                                | -225  | -175  | -125  | ^     |  |

| I <sub>SS</sub>        | Source current on ISS pin                     | V <sub>SS</sub> = 1.35 V                                               | -5.5  | -5    | -4.5  | μA    |  |

www.ti.com

# ELECTRICAL CHARACTERISTICS (continued)

over operating free-air temperature range,  $-40^{\circ}C < T_A < 125^{\circ}C$ ,  $T_J = T_A$ , VCC = 12 V, GND = 0 V,  $R_{RT} = 4.7 \text{ k}\Omega$ ,  $R_{DT} = 16.9 \text{ k}\Omega$ ,  $C_{VCC} = 1 \mu$ F, (unless otherwise noted)

| SYMBOL                | PARAMETER                                                        | TEST CONDITIONS                                         | MIN  | TYP  | MAX  | UNITS |

|-----------------------|------------------------------------------------------------------|---------------------------------------------------------|------|------|------|-------|

| Peak Curre            | ent Limit                                                        |                                                         |      |      |      |       |

| V <sub>OC1(off)</sub> | Level 1 over current threshold – $V_{OC}$ rising                 |                                                         | 0.9  | 1    | 1.1  |       |

| V <sub>OC2(off)</sub> | Level 2 over current latch threshold<br>– V <sub>OC</sub> rising |                                                         | 1.8  | 2.0  | 2.2  | V     |

| V <sub>OC1(on)</sub>  | Level 1 over current threshold – V <sub>OC</sub> falling         |                                                         | 0.5  | 0.6  | 0.7  |       |

| T <sub>d_OC</sub>     | Propagation delay                                                |                                                         | 60   | 200  | 500  | ns    |

| l <sub>oc</sub>       | OC bias current                                                  | V <sub>OC</sub> = 0.8 V                                 | -200 |      | 200  | nA    |

| Gate Drive            |                                                                  |                                                         |      |      |      |       |

|                       | GD1, GD2 output voltage high                                     | I <sub>GD1</sub> , I <sub>GD2</sub> = −20 mA            | 9    |      | 11   | V     |

|                       | GD1, GD2 on resistance high                                      | I <sub>GD1</sub> , I <sub>GD2</sub> = −20 mA            |      | 12   | 30   | Ω     |

|                       | GD1, GD2 output voltage low                                      | $I_{GD1}$ , $I_{GD2}$ = 20 mA                           |      | 0.08 | 0.2  | V     |

|                       | GD1, GD2 on resistance low                                       | $I_{GD1}$ , $I_{GD2}$ = 20 mA                           |      | 4    | 10   | Ω     |

|                       | Rise time GDx                                                    | 1 V to 9 V, C <sub>LOAD</sub> = 1 nF                    |      | 18   | 35   |       |

|                       | Fall time GDx                                                    | 9 V to 1 V, C <sub>LOAD</sub> = 1 nF                    |      | 12   | 25   | ns    |

|                       | GD1, GD2 output voltage during<br>UVLO                           | VCC = 6 V, I <sub>GD1</sub> , I <sub>GD2</sub> = 1.2 mA | 0.5  |      | 1.75 | V     |

| Thermal Sh            | nutdown                                                          |                                                         |      |      |      |       |

|                       | Thermal shutdown threshold                                       |                                                         |      | 160  |      |       |

|                       | Thermal shutdown recovery threshold                              |                                                         |      | 140  |      | °C    |

#### SLUS846A-SEPTEMBER 2008-REVISED MARCH 2009

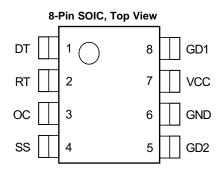

### **DEVICE INFORMATION**

### **TERMINAL FUNCTIONS**

|      | TERMINAL |     | DECODIDITION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|------|----------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME | NO.      | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| DT   | 1        | I   | This pin sets the dead time of high-side and low-side switch driving signals. Connect a resistor to ground. With internal 2.25-V voltage reference, the current flowing through the resistor sets the dead time. To prevent shoot through when this pin is accidentally short to ground, the minimum dead time is set to 120 ns. Any dead time setting less than 120 ns will automatically have 120-ns dead time.                                                                                                                                             |  |

| RT   | 2        | I   | The current flowing out of this pin sets the frequency of the gate driver signals.<br>Connect the opto-coupler collector to this pin to control the switching frequency for<br>regulation purpose. Parallel a resistor to ground to set the minimum current flowing<br>out of the pin and set the minimum switching frequency. To set the maximum<br>switching frequency limiting, simply series a resistor with the opto-coupler transistor.<br>This resistor sets the maximum current flowing out of the pin and limits the maximum<br>switching frequency. |  |

| ос   | 3        | I   | Over-current protection pin. When the voltage on this pin is above 1 V, gate driver signals are actively pulled low. After the voltage falls below 0.6 V, the gate driver signal recovers with soft start. When OC pin voltage is above 2 V, the device is latched off. Bringing VCC below UVLO level resets the overcurrent latch off.                                                                                                                                                                                                                       |  |

| SS   | 4        | I   | Soft-start pin. This pin sets the soft-start time of the system. Connect a capacitor to ground. Pulling this pin below 1 V will disable the device to allow easy ON/OFF control. The soft-start function is enabled after all fault conditions, including bias supply OV, UVLO, over-current protection and over-temperature protection.                                                                                                                                                                                                                      |  |

| GD1  | 8        | 0   | High-side and low-side switch gate driver. Connect gate driver transformer primary                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| GD2  | 5        | 0   | side to these two pins to drive the half bridge.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| GND  | 6        | -   | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| VCC  | 7        | -   | Bias Supply. Connect this pin to a power supply less than 20 V. Parallel a $1\text{-}\mu\text{F}$ capacitor to ground to filter out noise.                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

TEXAS INSTRUMENTS

www.ti.com

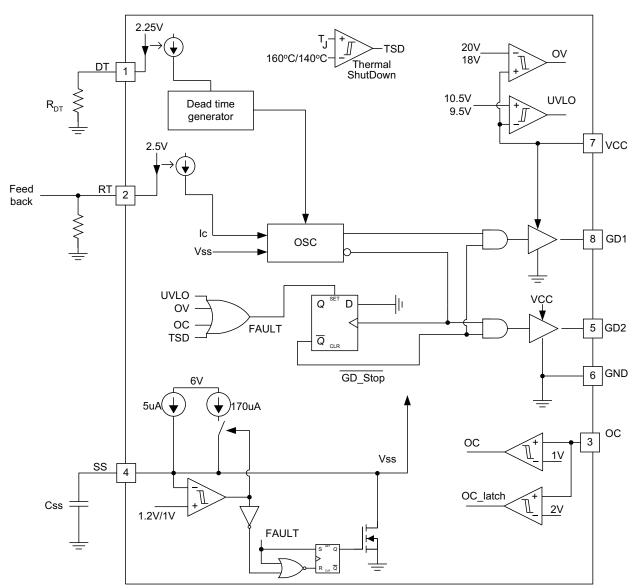

### Block Diagram

**EXAS**

**INSTRUMENTS**

# UCC25600

SLUS846A-SEPTEMBER 2008-REVISED MARCH 2009

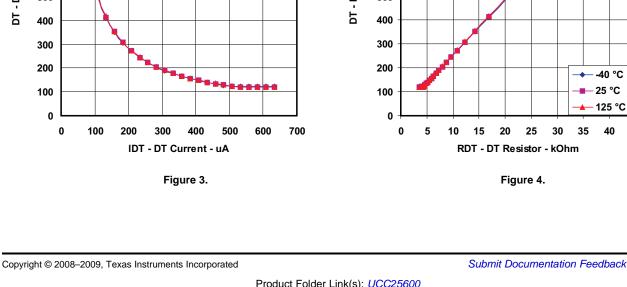

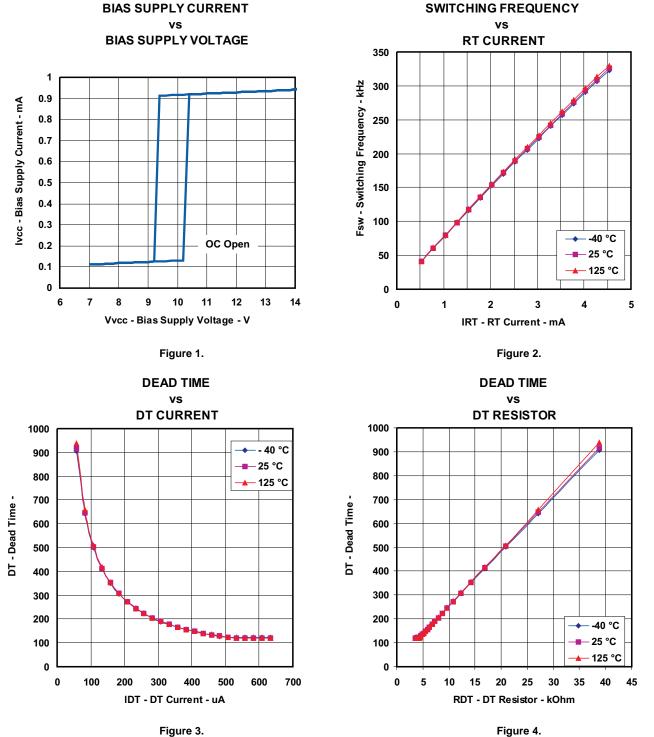

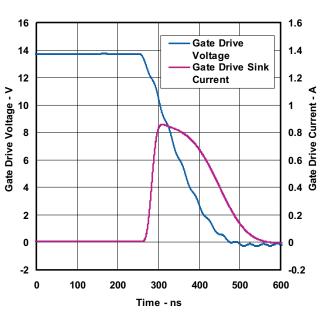

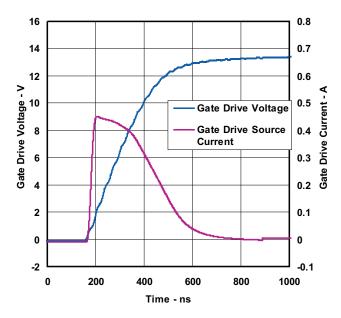

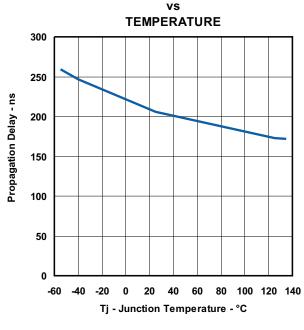

### **TYPICAL CHARACTERISTICS**

At V<sub>CC</sub> = 12 V, R<sub>RT</sub> = 4.7 k $\Omega$ , R<sub>DT</sub> = 16.9 k $\Omega$ , V<sub>SS</sub> = 5 V, V<sub>OC</sub> = 0 V; all voltages are with respect to GND, T<sub>J</sub> = T<sub>A</sub> = 25°C, unless otherwise noted.

### **TYPICAL CHARACTERISTICS (continued)**

Figure 5.

**OC PROPAGATION DELAY**

#### GATE DRIVE FALLING; VCC=15V

GATE DRIVE RISING; VCC=15V

Figure 6.

vs TEMPERATURE

Figure 8.

### **TYPICAL CHARACTERISTICS (continued)**

#### Figure 9.

Figure 10.

www.ti.com

### APPLICATION INFORMATION

### **Principal of Operation**

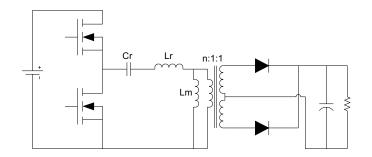

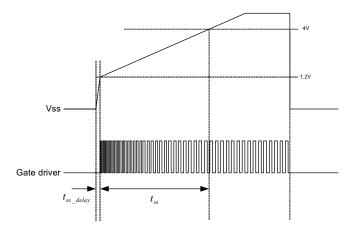

The soft-switching capability, high efficiency and long holdup time make the LLC resonant converter attractive for many applications, such as digital TV, ac/dc adapters and computer power supplies. Figure 12 shows the schematic of the LLC resonant converter.

Figure 12. LLC Resonant Converter

The LLC resonant converter is based on the Series Resonant Converter (SRC). By utilizing the transformer magnetizing inductor, zero-voltage switching can be achieved over a wide range of input voltage and load. As a result of multiple resonances, zero-voltage switching can be maintained even when the switching frequency is higher or lower than resonant frequency. This simplifies the converter design to avoid the zero-current switching region, which can lead to system damage. The converter achieves the best efficiency when operated close to its resonant frequency at a nominal input voltage. As the switching frequency is lowered the voltage gain is significantly increased. This allows the converter to maintain regulation when the input voltage falls low. These features make the converter ideally suited to operate from the output of a high-voltage boost PFC pre-regulator, allowing it to hold up through brief periods of ac line-voltage dropout.

Due to the nature of resonant converter, all the voltages and currents on the resonant components are approximately sinusoidal. The gain characteristic of LLC resonant converter is analyzed based on the First Harmonic Approximation (FHA), which means all the voltages and currents are treated as sinusoidal shape with the frequency same as switching frequency.

According to the operation principle of the converter, the LLC resonant converter can be draw as the equivalent circuit as shown in Figure 13.

Figure 13. LLC Resonant Converter Equivalent Circuit

#### SLUS846A-SEPTEMBER 2008-REVISED MARCH 2009

In this equivalent circuit, the  $V_{ge}$  and  $V_{oe}$  are the fundamental harmonics of the voltage generated by the half bridge and the voltage on the transformer primary side, respectively. These voltages can be calculated through Fourier analysis. The load resistor  $R_e$  is the equivalent resistor of the load, and it can be calculated as:

$$R_e = \frac{8}{\pi^2} n^2 R \tag{1}$$

Based on this equivalent circuit, the converter gain at different switching frequencies can be calculated as:

$$\frac{V_o}{V_{DC} / 2} = \frac{\frac{j\omega L_m R_e}{j\omega L_m + R_e}}{\frac{j\omega L_m R_e}{j\omega L_m + R_e} + \frac{1}{j\omega C_r} + j\omega L_r}$$

(2)

In this equation  $V_{DC}/2$  is the equivalent input voltage due to the half bridge structure.

#### **Table 1. Circuit Definition Calculations**

| NORMALIZED GAIN              | RESONANT<br>FREQUENCY                 | QUALITY FACTOR                       | NORMALIZED<br>FREQUENCY | INDUCTOR RATIO          |

|------------------------------|---------------------------------------|--------------------------------------|-------------------------|-------------------------|

| $M = \frac{V_o}{V_{DC} / 2}$ | $f_0 = \frac{1}{2\pi \sqrt{L_r C_r}}$ | $Q_e = \frac{\sqrt{L_r / C_r}}{R_e}$ | $f_n = \frac{f}{f_0}$   | $L_n = \frac{L_m}{L_r}$ |

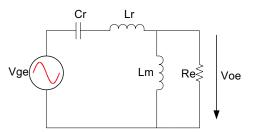

Following the definitions in Table 1, the converter gain at different switching frequencies can be written as:

$$M = \left| \frac{L_n f_n^2}{L_n f_n^2 + (f_n - 1)(f_n + 1 + j f_n L_n Q_e)} \right|$$

(3)

Because of the FHA, this gain equation is an approximation. When the switching frequency moves away from the resonant frequency, the error becomes larger. However, this equation can be used as the design tool. The final results need to be verified by the time based simulation or hardware test.

SLUS846A-SEPTEMBER 2008-REVISED MARCH 2009

From Equation 3, when switching frequency is equal to resonant frequency,  $f_n = 1$  and converter voltage gain is equal to 1. Converter gain at different loads and inductor ratio conditions are shown in Figure 14 through Figure 17.

Based on its theory of operation the LLC resonant converter is controlled through Pulse Frequency Modulation (PFM). The output voltage is regulated by adjusting the switching frequency according to the input and output conditions. Optimal efficiency is achieved at the nominal input voltage by setting the switching frequency close to the resonant frequency. When the input voltage droops low the switching frequency is decreased to boost the gain and maintain regulation.

The UCC25600 resonant half-bridge controller uses variable switching frequency control to adjust the resonant tank impedance and regulate output voltage. This 8-pin package device integrates the critical functions for optimizing the system performance while greatly simplifying the design and layout.

#### www.ti.com

#### Adjustable Dead Time

Resonant half-bridge converter relies on the resonant tank current at MOSFETs turn-off to achieve soft switching and reduce switching loss. Higher turn-off current provides more energy to discharge the junction capacitor, while it generates more turn-off loss. Smaller turn-off current reduces turn-off loss, but it requires longer time to discharge MOSFETs junction capacitors and achieve soft switching. By choosing an appropriate dead time, turn-off current is minimized while still maintaining zero-voltage switching, and best system performance is realized.

In UCC25600, dead time can be adjusted through a single resistor from DT pin to ground. With internal 2.25-V voltage reference, the current flow through the resistor sets the dead time.

$$t_d = 20ns + R_{dt} \times 24ns / k\Omega$$

(4)

To prevent shoot through when DT pin accidentally connects to ground, a minimum 120-ns dead time is inserted into the two gate driver outputs. Any dead-time setting less than 120-ns, will be limited to 120-ns.

### Oscillator

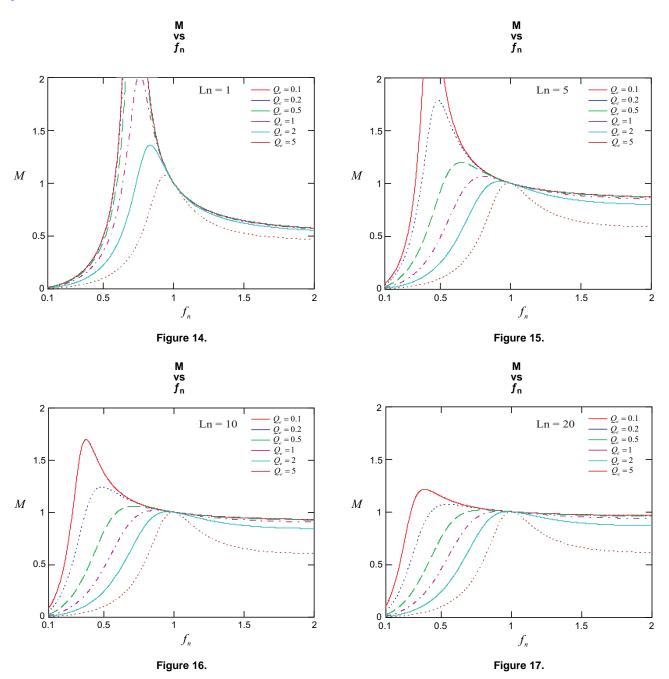

With variable switching frequency control, UCC25600 relies on the internal oscillator to vary the switching frequency. The oscillator is controlled by the current flowing out of RT pin. Except during soft start, the relationship between the gate signal frequency and the current flowing out of RT pin can be represented as:

$$f_{s} = \frac{1}{2} \frac{1}{\frac{6ns \times 1A}{I_{RT}} + 150ns} \approx I_{RT} \times 83Hz / \mu A$$

(5)

Since the switching frequency is proportional to the current, by limiting the maximum and minimum current flowing out of RT pin, the minimum and maximum switching frequency of the converter could be easily limited. As shown in Figure 18, putting a resistor from RT pin to ground limits the minimum current and putting a resistor in series with the opto-coupler limits the maximum current.

### Figure 18. Maximum and Minimum Frequency Setting for UCC25600

The frequency limiting resistor can be calculated based on following equations.

$$I_{f max} = \frac{6ns}{\frac{1}{2f_{max}} - 150ns}$$

(6)

$$I_{f min} = \frac{6ns}{\frac{1}{2f_{min}} - 150ns}$$

(7)

$$I_{f max} = 2.5V \left(\frac{1}{R_1} + \frac{1}{R_2}\right)$$

(8)

$$I_{f min} = \frac{2.5V}{R_2}$$

(9)

### Soft Start

During start up and fault recovery conditions, soft start is always implemented to prevent excessive resonant tank current and ensure Zero-Voltage Switching (ZVS). During soft start, the switching frequency is increased. The soft-start time can be programmed by placing a capacitor from SS pin to ground.

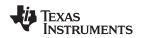

The soft-start pin also serves as an ON/OFF control pin of the device. By actively pulling the SS pin below 1 V, the device is disabled. When the pull down is removed, SS pin voltage is increased because of internal charging current. Once SS pin becomes above 1.2 V, the device starts to generated gate-driver signal and enters soft-start mode. The time sequence of soft start is shown in Figure 19.

Figure 19. Soft-Start Sequence

To prevent a long delay between the ON command and apperance of a gate driver signal, the SS pin current is set as two different levels. When SS pin voltage is below 1.2 V. its output current is 175 uA. This high current could charge the soft-start pin capacitor to 1.2 V in a short period of time, and reduces the time delay. This time delay can be calculated using following equation:

$$t_{SS\_delay} = \frac{1.2V}{175\mu A} C_{SS} \tag{10}$$

The switching frequency during soft start is determined by both the current flowing out of the RT pin and the voltage on SS pin. The switching frequency can be calculated based on the following equation:

$$f_{s} = \frac{1}{2} \frac{1}{\frac{6ns \times 1A}{I_{RT} + \left(1.81mA - \frac{V_{SS}}{2.2k\Omega}\right)} + 150ns}}$$

(11)

After SS pin voltage reaches 4 V, soft-start period is finished and switching frequency becomes the same as demanded by the RT pin current. The time used to charge SS pin from 1.2 V to 4 V is defined as soft-start time and can be calculated as:

$$t_{SS} = \frac{2.8V}{5\mu A} C_{SS} \tag{12}$$

To ensure reliable operation, the gate drivers restart with GD2 turning high. This prevents uncertainty during system start up.

www.ti.com

### **Burst-Mode Operation**

During light load condition, the resonant converter tends to increase its switching frequency and maintain the output voltage regulation. However, due to ringing caused by transformer parasitic capacitor and the rectification-diode-junction capacitors, the energy could be directly transferred to the load through these capacitors. When this power becomes more than the load requires, output voltage become higher than the regulation level. In this case, further increasing the switching frequency will not help the situation because energy transfer to the load is not through the power stage itself.

To prevent output over voltage during this condition, the UCC25600 includes the burst-mode operation function. When the control loop demands switching frequency higher than 350 kHz, the gate driver is disabled and the power stage stops switching. When the output voltage drops, the control loop begins to demand switching frequency less than 330 kHz, the gate driver recovers and the power stage begins to deliver power again. This allows output voltage to be regulated.

This burst mode can be easily disabled by limiting the maximum switching frequency to less than 350 kHz. In this way, the control loop will never demand a switching frequency higher than 350kHz and burst mode operation will not occur.

#### www.ti.com

#### **Over-Current Protection**

To prevent power stage failure under excessive load current condition, the UCC25600 includes an over-current protection function. With a dedicated OC pin, the power stage is shut down when OC pin voltage is above 1 V. Once the OC pin voltage becomes lower than 0.6 V, the gate driver recovers with soft start. To enhance system safety, the UCC25600 latches up the whole system when OC pin becomes above 2 V. Bring VCC below UVLO level to reset the device.

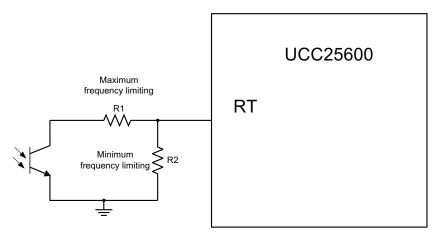

The current can be indirectly sensed through the voltage across resonant capacitor by using the sensing network shown in Figure 20.

Figure 20. Current Sensing for LLC Resonant Converter

The general concept of this sensing method is that, ac voltage across the resonant capacitor is proportional to load current.

According to the FHA model, peak voltage of the ac component on the resonant capacitor can be calculated as:

$$V_{Cr_pk} = \frac{4}{\pi} n V_o \left| \frac{j f_n L_n Q_e + 1}{f_n^2 L_n} \right|$$

(13)

Therefore, the resonant capacitor voltage reaches its maximum value at the minimum switching frequency and maximum load. According to this equation, the current sensing network components can be calculated. Due to the nature of FHA, the final circuit parameters need to be verified through actual hardware test.

#### **Calculated Current Sensing Network Components**

| NAME           | FUNCTION                                                             | DESIGN EQUATION                                      |

|----------------|----------------------------------------------------------------------|------------------------------------------------------|

| R <sub>S</sub> | Transfer ac voltage across resonant<br>capacitor into current source | $R_{s} = \frac{V_{Cr_{pk}} (max)^{2}}{2P_{Rs}(max)}$ |

| C <sub>S</sub> | Blocking dc voltage on resonant capacitor                            | $C_s = \frac{10}{R_s f_{\min}}$                      |

| R <sub>P</sub> | Load resistor of the current source                                  | $R_{p} = \frac{R_{s}}{V_{Cr_{pk}}(max)}\pi$          |

| Ср             | Filter capacitor                                                     | $C_p = \frac{10}{R_p f_{\min}}$                      |

### **Gate Driver**

Half-bridge resonant converter is controlled by the nearly 50% duty cycle variable frequency square wave voltage. This allows the half bridge to be easily driven by the gate-driver transformer. Compared with a half-bridge driver device, a gate-driver transformer provides a simple and reliable solution, which:

- Eliminate the need for gate driver power supply

- Enable simplified layout

- Preventing shoot through due to the transformer coupling

- No latch up

The UCC25600 integrates two-gate drivers with 0.4-A source and 0.8-A sink capability to directly drive the gate driver transformer.

For LLC resonant converter, it is critical for the gate-driver signal to be precisely symmetrical. Otherwise, the resonant tank operation will be asymmetrical. The load current distribution will be unbalanced for the output rectifiers, which in turn requires over design of the power stages and thermal management.

In UCC25600, the gate-driver outputs are precisely trimmed to have less than 50 ns mismatch. Although the gate-driver signal is quite symmetrical, it is still recommended to insert the dc blocking capacitor in the gate-driver transformer primary side to prevent transformer saturation during fast transients.

### VCC

Connect a regulated bias supply to VCC pin. When VCC becomes above 10.5 V the device is enabled and after all fault conditions are cleared the gate driver starts with soft start. When VCC drops below 9.5 V, the device enters UVLO protection mode and both gate drivers are actively pulled low. When VCC rises above 20 V the device enters VCC over-voltage protection mode and the device is disabled with both gate drivers actively pulled low. VCC over-voltage protection will recover with soft start when VCC voltage returns below 18 V.

#### **Over-Temperature Protection**

UCC25600 continuously senses its junction temperature. When its junction temperature rises above 160°C the device will enter over-temperature protection mode with both gate drivers actively pulled low. When junction temperature drops below 140°C, gate driver restarts with soft start.

### PACKAGING INFORMATION

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | e Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|------|----------------|---------------------------|------------------|------------------------------|

| UCC25600D        | ACTIVE                | SOIC            | D                  | 8    | 75             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| UCC25600DR       | ACTIVE                | SOIC            | D                  | 8    | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| UCC25600DRG4     | ACTIVE                | SOIC            | D                  | 8    | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details. TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(3)</sup> MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

TEXAS INSTRUMENTS www.ti.com

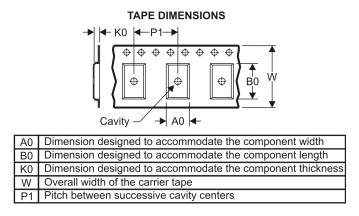

### TAPE AND REEL INFORMATION

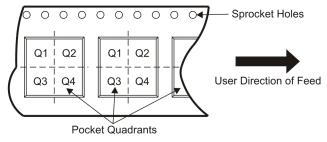

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal | *All | dimensions | are | nominal |

|-----------------------------|------|------------|-----|---------|

|-----------------------------|------|------------|-----|---------|

| Device     | Package<br>Type | Package<br>Drawing |   |      | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|------------|-----------------|--------------------|---|------|--------------------------|--------------------------|---------|---------|---------|------------|-----------|------------------|

| UCC25600DR | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4     | 5.2     | 2.1     | 8.0        | 12.0      | Q1               |

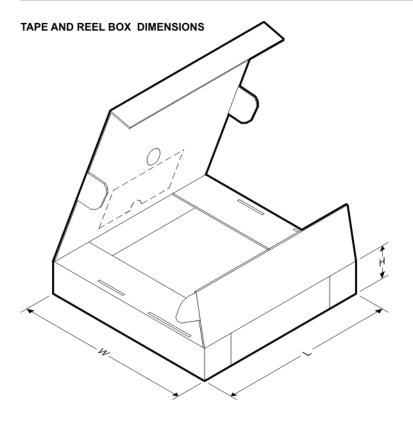

# PACKAGE MATERIALS INFORMATION

6-Mar-2009

\*All dimensions are nominal

| Device     | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|------------|--------------|-----------------|------|------|-------------|------------|-------------|

| UCC25600DR | SOIC         | D               | 8    | 2500 | 340.5       | 338.1      | 20.6        |

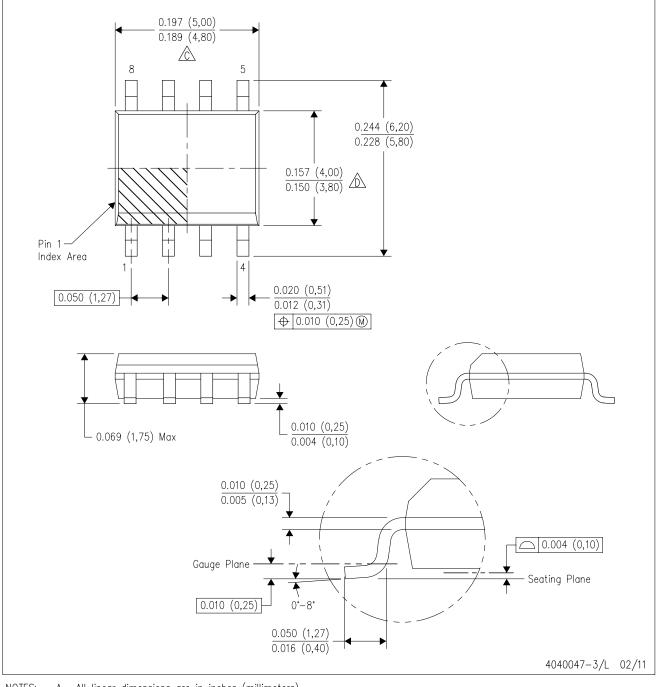

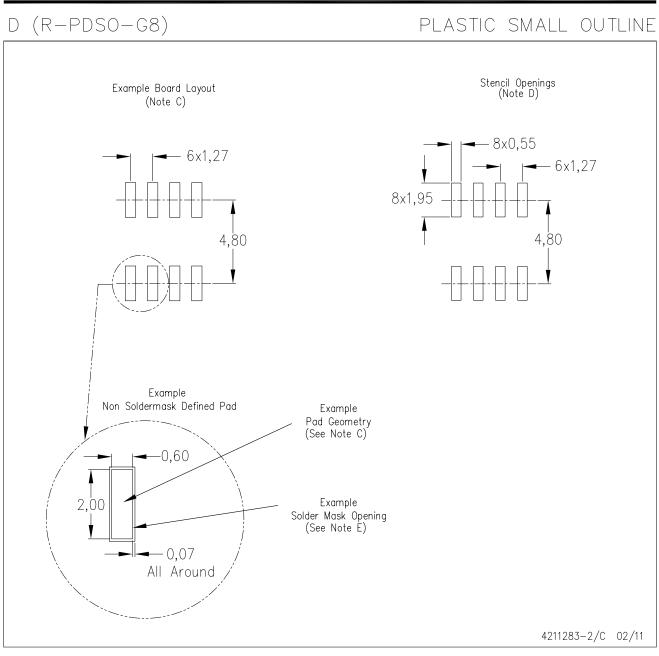

D (R-PDSO-G8)

PLASTIC SMALL OUTLINE

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.006 (0,15) each side.

- Body width does not include interlead flash. Interlead flash shall not exceed 0.017 (0,43) each side.

- E. Reference JEDEC MS-012 variation AA.

# LAND PATTERN DATA

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC-7525 for other stencil recommendations.

E. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products                    |                        | Applications                     |                                   |

|-----------------------------|------------------------|----------------------------------|-----------------------------------|

| Audio                       | www.ti.com/audio       | Communications and Telecom       | www.ti.com/communications         |

| Amplifiers                  | amplifier.ti.com       | Computers and Peripherals        | www.ti.com/computers              |

| Data Converters             | dataconverter.ti.com   | Consumer Electronics             | www.ti.com/consumer-apps          |

| DLP® Products               | www.dlp.com            | Energy and Lighting              | www.ti.com/energy                 |

| DSP                         | dsp.ti.com             | Industrial                       | www.ti.com/industrial             |

| Clocks and Timers           | www.ti.com/clocks      | Medical                          | www.ti.com/medical                |

| Interface                   | interface.ti.com       | Security                         | www.ti.com/security               |

| Logic                       | logic.ti.com           | Space, Avionics and Defense      | www.ti.com/space-avionics-defense |

| Power Mgmt                  | power.ti.com           | Transportation and<br>Automotive | www.ti.com/automotive             |

| Microcontrollers            | microcontroller.ti.com | Video and Imaging                | www.ti.com/video                  |

| RFID                        | www.ti-rfid.com        | Wireless                         | www.ti.com/wireless-apps          |

| RF/IF and ZigBee® Solutions | www.ti.com/lprf        |                                  |                                   |

**TI E2E Community Home Page**

e2e.ti.com

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2011, Texas Instruments Incorporated